## FPGA Accelerated CME Tick-To-Trade System

## Description

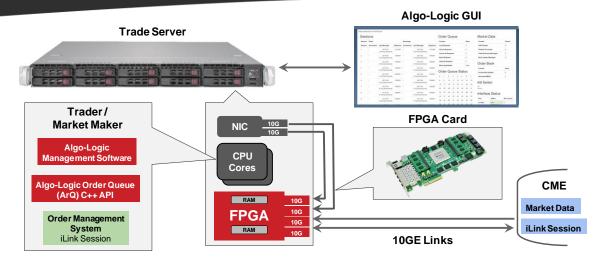

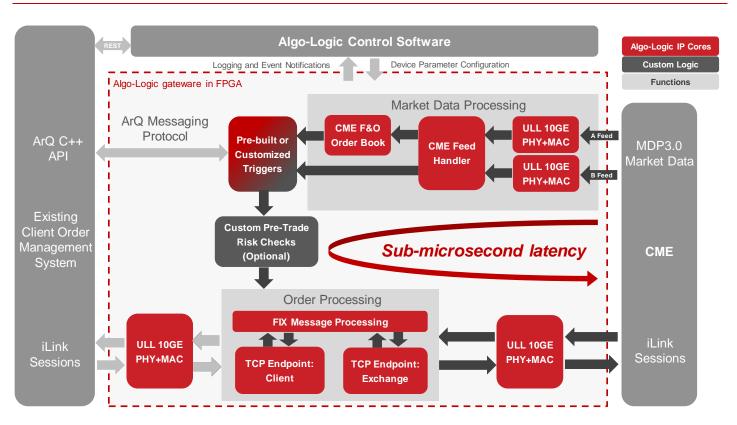

Algo-Logic Systems' 4th generation FPGA accelerated Gateware Defined Networking® (GDN) CME Tick-To-Trade (T2T) System is a sub-microsecond trading solution. It supports all CME Group exchanges including CBOT, COMEX, and NYMEX. The solution is built using Algo-Logic Systems' internally developed, pre-built IP cores that significantly reduce time-to-market and provide flexibility for customizations.

Sub-microsecond wire-to-wire latencies are achieved by receiving CME MDP 3.0 tick data directly into the FPGA on a 10G link, detecting opportunities, and placing trades in form of FIX messages encapsulated in TCP packets using the ultra-low latency (ULL) 10G TCP Endpoint.

The CME T2T system includes new parametrized triggers for mass quote cancel, mass action request and hedging as well as the ability to modify FIX order fields in FPGA logic. It seamlessly integrates with existing Order Management Systems (OMS) through C++ Application Programing Interfaces (APIs). A Graphical User Interface (GUI) and RESTful APIs are provided for control and monitoring of the accelerator.

#### ArQ C++ Library and API:

- Low latency C++ 98 compatible APIs are used to set up triggers and preload FIX orders to be injected

- Well defined API to pass trigger parameters between hardware and software

### **Control Software includes:**

- Device parameter configuration (i.e., IP and MAC addresses) and status monitoring

- Logging and event notifications

## **FPGA-Accelerated Trading**

#### Quote Cancellation

Ultra-low-latency mass quote cancellation by product, instrument group or each instrument

### Hedging

Instantly react to order fills to inject hedge order

#### Spreading

- Ultra-low-latency top of book updates

- Single API call for immediate injection of preloaded quote or hedge order with modified price, quantity, and order IDs

- Auto-reload enables multiple hedges and quotes to be sent using pre-loaded FIX order

- Allows trading on multiple instruments with simultaneous multi-leg strategies

- Supports hybrid strategies with low-latency interface between hardware and software

## **Short Time to Market**

#### Algo-Logic's prebuilt IP cores with sub-microsecond latency

- ULL 10GE PHY+MAC

- CME Feed Handler

- CME Futures & Options Order Book

- 10G TCP Endpoint

- FIX Message Processing

#### **Augments existing Order Management Systems**

- Minimal changes to software through well-defined APIs

- No FPGA programming skills required

# FPGA Accelerated CME Tick-To-Trade System

## CME Tick-To-Trade System Features and Base Specifications

| FPGA Accelerated Trading                           | Quote cancel, hedging, multi-leg spreading                                                 |

|----------------------------------------------------|--------------------------------------------------------------------------------------------|

| Pre-Built IP Cores                                 | CME Feed Handler, CME Futures & Options Order Book, 10G TCP Endpoint, ULL 10GE PHY+MAC     |

| Multicast Channels for Market Data                 | Up to 16                                                                                   |

| Order Book Configuration                           | 20 security IDs with L2 snapshots containing BBO, all 10 book levels                       |

| FIX Sessions and Order Queues                      | 32 and 64 respectively, with 2 Kbyte per queue message size limit                          |

| Optional Pre-Trade Risk Checks (Customer Provided) | Session based limits, Max Shares per Order, Order Value limits, and Number of Order limits |

| Logging and Event Notifications                    | FIX logs, Raw Market Data logs, CME Order Book BBO, Trigger events                         |

| FPGA Device and Platform                           | Intel Stratix V with 10 Gbps Ethernet on Terasic DE5-Net                                   |

## CME Tick-To-Trade System Diagram

Algo-Logic Systems builds FPGA accelerated Gateware Defined Networking® (GDN) latency.